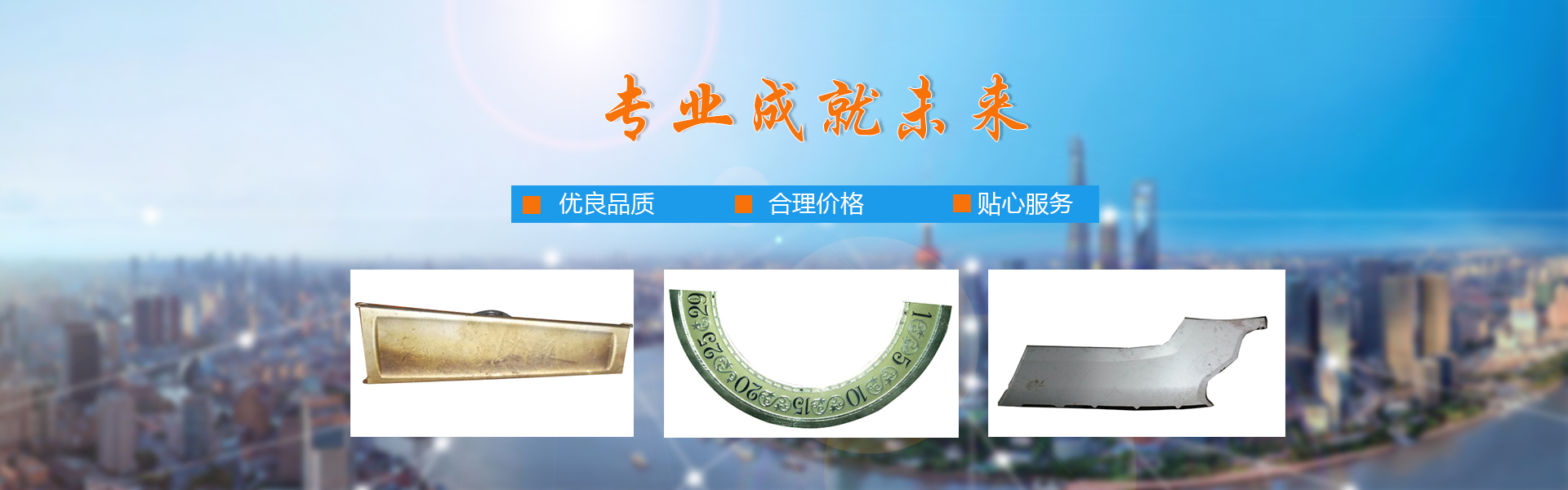

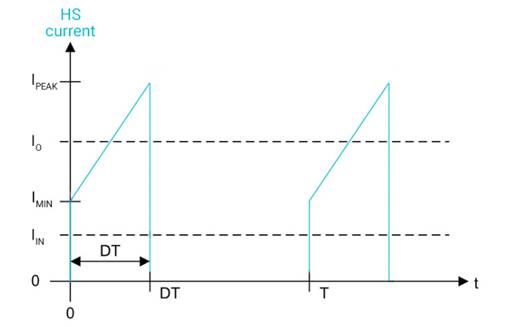

���C��Ч�;o�����OӋͬ�r���؇��H�o��늸ɔ_�eί�T�� (CISPR) �ȽM������ć���늴Ÿɔ_ (EMI) Ҫ����һ�������ˣ�Ԫ�����x��ɞ����OӋ�^�̵��P�I���c������OӋ�Q��һ�ӣ��ڲ�ͬ�M��֮�g�M���x������ǚw�Y����������P�I�OӋĿ�˵ę���u�����Ը�Ч�����õğ��������Q��buck��������ͨ������ҕ�齵��늴Ÿɔ_���x헡����\���ǣ����ж�N�x������ʹ�������a����EMI�����\���ǣ���Ȼ�ж�N��ʩ���Ԝp���@�������������늴Ÿɔ_���D1��buck��������ʾ��D��

�D1. Buck������ʾ��D

�·�岼��ע�����

���OӋ��횷���EMIҪ��r�������x���m���ğoԴԪ��ֵ�Դ_�������OӋ֮�⣬�·�岼�֑�ԓ���M���OӋ�r��Ҫ���]����Ҫ���ء��Ѓɂ�buck�������·�岼��ͨ��Ҏ�t�Ɍ�늴Ÿɔ_������ͣ�

• ʹݔ������������e������M���ܵؿ��������·��VIN��GND���_��������ȵp�ٸ�˲�B��� (di/dt) �h·��e��

• ͨ�^��С���_�P���c����e����С����˲�B늉� (dv/dt) ���c�ı���e��

����ݔ�������

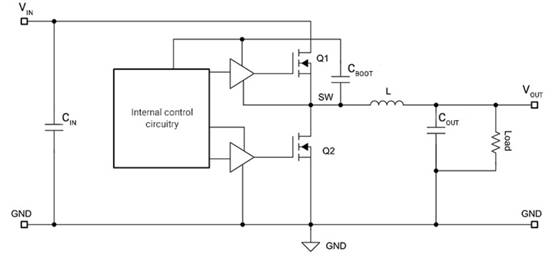

��EMIҪ������֮���M���_�P���������OӋ�r���pС��˲�B����h·����e�dz���Ҫ����buck�������У���Ҫ��EMI�ĽǶȿ��]ݔ��늉����حh·��buck������ͨ�^�_�����P�]�c�Դ���_�P�������^�ߵ�ֱ��늉������^�͵�늉����Ķ��ڸ߉��Ȯa��MOSFET�������D 2 ��ʾ��

�D2. Buck�����������µ�ݔ�����׃��

MOSFET�����_�����P�]���a����ݔ��������ṩ�ķdz����J�Ҏ����B�m��������T��TI��3-A LMQ66430-Q1��6-A LMQ61460-Q1 36V buck���������ڷ��b�ȼ��ɸ��lݔ����������Ķ����F��ݔ������h·��e����С�����pСݔ�������·��e������ݔ��˵ļ���늸и�С���Ķ��p��늴�������ݔ����

�������e���

��Ҫ���]����һ����˲�B����h·�������e��ݭh·�����e���ؓ؟���_�P������ͨ���g��߉���MOSFET�ŘO�ṩ�ӡ��Ȳ��·���P�����g��ԓ��������³�늡��߉���MOSFET��Դ�O�B�����_�P���c������GND�������e����B�ӵ�MOSFET��Դ�O���_�ɴ_����Դ늉� (VGS) �������_��MOSFET�����ڴ����buck��������������·��������һЩ���õ��_�P���c�^����B�����e��������M���@����С���_�P���c�Ԝp��EMI�^����ֻ���յ��m���䷴��Ч�����ڷ��b�ȼ������e��ݵ�LMQ66430-Q1���H��ѭ֮ǰ�ᵽ�ăɂ�Ҏ�t��ͬ�r߀�p���ˌ��ⲿ�M��������

���Y

�ڇ����EMIҪ���±��ֽY���o�����Դ�OӋ���F�������ܺ����y�����м����������buck����������ʹ����EMIҪ����OӋ���F���������ף�ͬ�r߀�����ڜp�����w�ⲿ�M���Ĕ����� |