�����S���O�乩���̡��аl�C���ȶ����аlһ�N�Q֮���~����I�ϣ�Hybrid bonding����ˇ���@헼��g�����Ƅ���һ�� 2.5D �� 3D ���b���g��

�c�F�еĶѯB���I�Ϸ�����ȣ�����I�Ͽ����ṩ���ߵĎ������͵Ĺ��ģ�������I�ϼ��gҲ���y���F��

�����������~����I�ϵ���Ҫ����

�~����I�ϲ��������r�£��� 2016 ���_ʼ��CMOS �D��������_ʼʹ�þ��A�g��Wafer-to-Wafer���Ļ���I�ϼ��g����aƷ�����w���ԣ������̕������aһ��߉���A��Ȼ�����aһ����������̎���ĆΪ����A��֮��ʹ���~���B���g���ɂ����A�Y����һ���ٌ���оƬ�г�СƬ���γ� CMOS �D���������

����I���c���M���b�Ĺ�����ʽ����ͬ����ǰ�߸����s�������������_�l��һ�N��ͬ��׃�w���Q����Ƭ�����A��Die-to-Wafer�����I�ϣ������ڃȲ�������������Ƭ�϶ѯB���I����Ƭ��KLA �����N�����O Stephen Hiebert ��ʾ�����҂����^�쵽��Ƭ�����A�Ļ���I�ϰlչ���ţ�����Ҫ�����������܉F��ͬ�ߴ�оƬ�Į������ɡ���

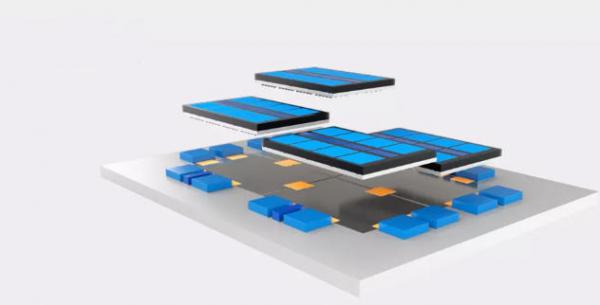

�@һ���������M���b��ߵ�һ���µ�ˮƽ���ڮ������M���b�����У������̿����ڷ��b�м��ɶ���Ƭ�� DRAM �ї�����ʹ�ìF�еĻ��B�����B����Ƭ��ͨ�^����I�ϣ�DRAM ��Ƭ����ʹ���~���B�ķ����ṩ���ߵĎ������@�N����Ҳ�������ڃȴ�ї����������M�ϵ�߉�С�

Xperi �Ľܳ����̎� Guilian Gao ����������v���f�����������m���ڲ�ͬ���õĝ��������� 3D DRAM���������ɺ�оƬ�ֽ⡣��

���^�@��һ험O�������ԵĹ�������Ƭ�����A�Ļ���I����Ҫԭʼ��оƬ�����M���O��������ļ��ɷ�������������������܉�M���@ЩҪ����ôԓ헼��g���ɞ��оƬ�OӋ���T���x��

���y�ϣ�����M�OӋ���I���_�l��Ƭ��ϵ�y��SoC�������ԿsСÿ�����в�ͬ���ܵĹ��c��Ȼ���ڌ��������b��ͬһ��Ƭ�ϣ������S�������c��׃��Խ��Խ���s�Ͱ��F����������D�����µ�����������ڂ��y�����M���b�нM�b���s��оƬ���ԔUչ���c��ʹ�û���I�ϵ����M���b�t����һ�N�x��

GlobalFoundry��Ӣ�ؠ������ǡ��_�e늺�늶����������~����I�Ϸ��b���g��Imec �� Leti Ҳ����ˡ����⣬Xperi �����_�lһ�N����I�ϼ��g������ԓ���g�S�ɽo������˾��

���� IC ���b���g����ɫ

IC ���b��ͱ��࣬���ַ��b�Ј��Ļ��B��ͣ����������I�ϡ����bоƬ�����A�����b��WLP����ֱͨ��ͨ�ף�TSV�������B�nj�һ��оƬ�B�ӵ����b�е���һ��оƬ��TSV �� I/O ������ߣ������ WLP�����bоƬ�������I�ϣ���ϻ��B�� TSV �ܶȸ��ߡ�

TechSearch �Q ������ķ��b��s�� 75% �� 80% �ǻ��������I�ϣ���ʹ�ú����C������һ��оƬ�ӵ���һ��оƬ������ϣ������I�϶�������Ʒ���b�ʹ惦����Ƭ�ѯB��

�ڵ��bоƬ�У�ʹ�ø��N��ˇ���E��оƬ픲��γɴ����ĺ����K��С���~�K��Ȼ���������D�����b�چΪ���оƬ����ϡ��K�����~���P�ϣ��γ��c�B�ӣ��Q֮�龧�A�I�ϙC��ϵ�y�I����Ƭ��

WLP ��ֱ���ھ��A���M�з��b�yԇ��֮�����и�Ɇ��w�M�����ȳ����A�����b��Fan-out WLP��Ҳ�Ǿ��A�����b�е�һ�N��Veeco ��һλ�ƌW�� Cliff McCold �� ECTC �����v���f�������� WLP �܉��M���^С�Ķ��S�B�ӣ��Ķ�����оƬ���·��ɵ��������e�ϣ���F���O���ṩ���ߵ� I/O �ܶȣ����ߵĎ��������ܡ���

TSV ���ڸ߶� 2.5D/3D ���b���� 2.5D ���b�У���Ƭ�ѯB�ڃȲ����ϣ��Ȳ����а��� TSV�����g�����B��оƬ���·��֮�g�Ę��������ṩ����� I/O �͎�����

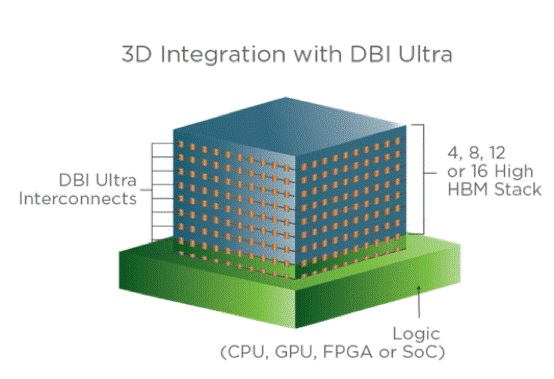

2.5D ���b�� 3D ���b����ͱ��࣬�ߎ����惦����HBM������һ�N 3D ���b��ͣ��@һ�����nj� DRAM ��Ƭ�ѯB��һ�𡣌�߉�ѯB��߉�ϻ�߉���ڃȴ��ϵķ���Ҳ���ڳ��F��Ӣ�ؠ��aƷ���ɿ��O Ramune Nagisetty ��ʾ��߉�ѯB��߉�ϵķ���߀�]���ռ���߉�ѯB�ڃȴ��ϵķ���Ŀǰ�����d��

�ڷ��b�У�Ŀǰ�����Pע����СоƬ��СоƬ��������һ�N���b��ͣ���оƬ�����̵Ď��п��ԓ���һ��ģ�K����Ƭ���NСоƬ���͑����Ի�ϴ����@ЩоƬ����ʹ�÷��b����Ƭ����Ƭ��Die-to-Die���Ļ��B�����M���B�ӡ�

СоƬ���Դ����ڬF�еķ��b��ͻ��µ��wϵ�ܘ��С����@��һ�N�ܘ��������� UMC���A��ӣ�ؓ؟�I���_�l�ĸ����� Walter Ng �f���������ڞ��΄�������Q�������@Щ��������ٶȡ����������ʵ����ܣ��Еr߀��Ҫ���]�ɱ����ء���

���������M�� 2.5D ���b�� 3D ���b�ǹ�������ʹ�õĬF�л��B�����;��A�I���������@Щ���b�У�ʹ���~�K���~���ѯB���B����Ƭ�����ں��Ӳ��ϣ��K��֧���ڲ�ͬ���O��֮�g�ṩС�����ٵ�늚��B�ӡ�

�����M�����K���g���� 40��m �� 36��m���@����g�����һ���Ŀ��g���x������ 40��m �g����� 25��m ���~������ 15 �Ŀ��g���x��

���ڼ��g���Ҫ�I��ʹ�ßቺ�s�B�ӣ�TCB������һ�� TCB �I����ȡ��һ�K��Ƭ���������K�c��һ�K��Ƭ���K���R�����É����͟������K�I�����������^��TCB �^�̾��������~�KҲ���ڱƽ�����O�ޡ�һ����ԣ�ҕ�O���g���� 20��m����Ҳ��һ�������ڇLԇ�����c�g�ࡣ

Imec �����_�lһ�Nʹ�� TCB ���F�� 10��m �g�༼�g��7��m �� 5��m Ҳ�����аl�С���40��m �K�g�������ĺ��Ӳ��ρ��a�����׃�������s�ŵ� 10��m ���С���g���r����r�����l��׃������ Imec �ĸ��ƌW�� Jaber Derakhshandeh ������� ECTC ���h�ϵ�һƪՓ�����f�����ڼ��g������У�����������õ��B��ȡ�Q�� TCB ���ߵľ��ȡ��eλ���Aб�Լ����ϵ�׃��������

�������L���K�İlչ������Imec �_�l��һ�N���ى|�幤ˇ��ͬ��ǰһ�ӣ���Ƭ����Ȼ�����K����ͬ���ǣ��� Imec ��ˇ�У���Ƭ��߀�мٽ����K���@��K�����֧�μܘ���С����

Derakhshandeh �f������ 3D ��Ƭ�����A�ĶѯB��������һ���ٽ����K���ԜpС TCB ���ߵăAб�`������ƺ���׃�Σ��Ķ�ʹճ����Ƭ��ͬλ�õ����ͳ��ν��^���|����ͬ������

����I���� TCB ���a��

��ijЩ�r�����K / ֧���� TCB ���ܕ��ù⣬�@�r�����Ҫ����I�ϣ��������������g���ں�����ڴ�ǰ���롣

���^���K�����ܿ����Ј�����ʧ�����K�ͻ���I�ϼ��g�������Ј���ռ��һϯ֮�أ��@ȡ�Q�ھ��w�đ��á�

Ŀǰ����I�ϼ��g���ڰlչ���_�e����аl�ԙ࣬�������о�һ�N��������оƬϵ�y��SoIC���ļ��g��ʹ�û���I�ϣ��_�e늵� SoIC ���g���Ԍ��F�������I���g�ࡣ��Ϥ��SoIC �ľ��_�|�g���ǬF�з����� 0.25 �������ܶȰ汾���Ԍ��F 10 �����ϵ�оƬ��оƬ��ͨ���ٶȣ����_�� 2000 ���Ď����ܶȺ� 20 ������ԴЧ�ʡ�

�_�e늵� SoIC Ӌ���� 2021 ��Ͷ�����a�����Ԍ��FС�g�� HBM �� SRAM �惦�����w�Լ���� 3D ��оƬ�ܘ����_�e��о��T MF Chen �������һƪՓ�����f���c���� HBM ��ȣ����^���� SoIC �� DRAM �惦�������w�����ṩ���ߵĴ惦���ܶȡ���������Ч�ʡ���

�_�e������_�lоƬ�����A��Chip-to-Wafer���Ļ���I�ϼ��g�����A�I���ѽ����C�ϵ�y��MEMS��������������ʹ�ö��꣬����ͱ��ࡣ����Ӻ��C�ϵ�y������ͷ��b��ه�ڃɂ������Ƭ���I�ϣ��� Brewer Science �ĸ��о����W�� Xiao Liu �f���������C�ϵ�y�������^���У��������A����ճ�ϵ���һ�����A�ϣ��Ա��o���е� MEMS �Y����ֱ���I�ϼ��g�����������I�Ϻ�ꖘO�I�ϣ����g���I�ϼ��g��������ٹ������ቺ�I�Ϻ��zճ���I�ϣ����dz��õķ�����ʹ���zճ������ɂ�����֮�g�����g�ӣ�̎��������`���

�~����I��������F�� 2016 �꣬���r���ጢ�@헼��g���� CMOS �D�������������ĬF�ڌ��� Xperi �� Ziptronix �@����ԓ���g���S�ɡ�

Xperi �ļ��g�Q��ֱ�ӽ������B��DBI����DBI �ڂ��y�ľ��A�S���M�У��������ھ��A�����A���I�Ϲ�ˇ�����@һ�^���У��Ȍ����A�M��̎����Ȼ���ٺ��P������棬ʹ����׃��ƽ����

���x���AҲ���v��Ƶ��^�̣���Ƭʹ�Ãɲ���ˇ�I�ϣ�������늽��|���B��Ȼ���ǽ��ٻ��B��

EV Group �I�հlչ���O Thomas Uhrmann ��ʾ�������w���ԣ����A�����A���O����������x��������������ˇ�����У����A��������ǰ�˾��A�S�h���С����@�N��r�£����ڻ���I�ϵľ��A�Ƃ��ڽ����OӋҎ�t���坍�ȡ������x���Լ�����͌��ʷ������R�T����������������ϵ��κ��w�������a�����w�������� 100 �� 1,000 ���Ŀ�϶����

�M����ˣ�ԓ���g�ѱ��C�������ڈD��������������O�������о��_�l�С�Uhrmann �f����Ӌ���Mһ���Ƴ��T��ѯB SRAM ��̎����оƬ֮���������

����I�ϵ� 3D ����

�~����I���Ƅ����M���b

�������MоƬ���b���I��߀��������Ƭ�����A����Ƭ����Ƭ���~����I�ϣ�������Ƭ�ѯB�ھ��A�ϡ�����Ƭ�ѯB���н���ϻ���Ƭ�ѯB����Ƭ�ϡ�

�@�Ⱦ��A�g�I�ϸ������y����������Ƭ�����A�Ļ���I�϶��ԣ�̎�������w������Ƭ�Ļ��A�Oʩ�Լ��I����Ƭ�������ɞ�һ��ش����𡣡� Uhrmann �f�����mȻ���ԏľ��A�����ƻ�Č�оƬ���Ľ����OӋ���A̎��������оƬ̎�������Դ����S������ͨ������˹�ˇ�������ЉK����Ƭ̎�����ڱ�Ĥ����ϵ���Ƭ��ݔ������m��ǰ���坍���e����������Ƭ���e�@���^�ߵ�ճ���ʡ���

Uhrmann �f�������A�����A���I�Ϸ�ʽ���ڰlչ�����ҿ����@�N��ʽ���^�̕r�����������_�l�ķ���r�����J���@��һ헷dz����s�ļ����΄գ������_�e��@�ӵĹ�˾�����Ƅ��@���ИI�İlչ���҂����Ԍ��䱧���ڴ�����

���b�Ļ���I���c���y�� IC ���b��ijЩ�����Dz�ͬ�ġ����y�ϣ�IC ���b����һ�� OSAT��Outsourced Semiconductor Assembly and Test��ί���y�����S������b�S���M�еģ����~����I�υs���ھ��A�S�ĝ��������M�У������� OSAT �С��c���y���b̎���ߴ�ȱ�ݲ�ͬ������I�ό�С�ļ{��ȱ�ݷdz����У���Ҫ���S���ĝ����ҁ���ֹСȱ�ݸɔ_���a�^�̡�

ȱ�ݿ������P��Ҫ��ِ����W�аl������ Tim Skunes �f�������]���@Щ��ˇʹ����֪�İ��F������Ƭ��ʧ���ɱ��ܸߡ��ڽM��֮�g����һЩͻ���γɴ�ֱ��늚��B�ӣ������K�߶Ⱥ����Ԍ��ڴ_���ѯB�M��֮�g�Ŀɿ������P��Ҫ����

���ϣ���֪����ģ�ߣ�KGD�����P��Ҫ��KGD �Ƿ��Ͻo��Ҏ���δ���b�������Ƭ������]�� KGD�����b�������ܵͮa��ʧ����

KGD �����b�SҲ����Ҫ�����҂��յ���Ƭ�������M�з��b�����������ܮaƷ����������Ҫ���҂��ṩ�dz��ߵĮa�������|��늚�̼��g�I�N���O�����t�������һ�λ���б�ʾ������ˣ��҂�ϣ�� KGD �܉��^��֜yԇ���������á���

��Ƭ�����A�Ļ���I������ھ��A�����A�Ĺ�ˇ�����ą^�e����оƬ���ø��ٵ��bоƬ�I�����Йz�y��������оƬ���и�ͶѯB�ġ�

Xperi ����Ƭ�����A����I�����̈D

�����^�̏ľ��A�S�_ʼ��ʹ�ø��N�O���ھ��A�ϼӹ�оƬ���@���ֱ��Q֮��ǰ�����a�£�FEOL�����ڻ���I���У��ɂ������ľ��A�������^���б��ӹ���֮���A���\�͵����a����ˣ�BEOL�������ⲿ�֣�ʹ�ò�ͬ���O�䌦���A�M�І�һ�Ƕ��ˇ��

��һ�Ƕ��ˇ��һ헳���ļ��g��ͨ���nj���������ϳ����ھ��A�ϣ�Ȼ����С��ͨ������������M���g�̲��L�ƈD�������ͨ�^���e��ˇ����~���^���ھ��A�������γ��~���B�P���~���P���מ��λ�������^���@һ�^���c�������M�ľ��A�SоƬ���a��ƣ������ڸ�оƬ���ԣ����ą^�e�����~���B�Ǽ{���e�ġ�

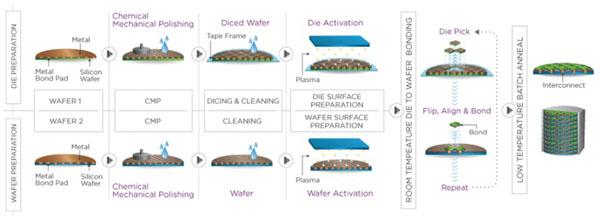

�������̾��� Xperi ������Ƭ�����A���~����I�Ϲ�ˇ�����ģʽ��������˾ʹ����ƻ��м���ͬ�����̡�

Xperi ���A�����A��ˇ�ĵ�һ����ʹ�û��W�Cе���⣨CMP�����⾧�A���棬��ͨ�^���W�����͙Cе����������档���@һ�^���У��~�����������ھ��A���棬�õ��\������İ��ۣ����^�õ����ʡ�

���^�����W�Cе���⣨CMP�����F�^�����y�������^�ȕ�ʹ�~���P�İ���̫����K���܌���ijЩ���P�o���Ӻͣ����ⲻ��t�������~��������ɶ�·��ᘌ��@һ���}��Xperi �_�l�� 200nm �� 300nm CMP ���ܡ�Xperi ���̲������� Laura Mirkarimi ��ʾ�������^ȥʮ���У�CMP ���g���O���OӋ�������x��ͱO�ط��涼�M���˄��£��܉��_�����ʿ��ƣ��^�̿��؏��Ҿ��з����ԡ���

�ڽ��^ CMP ֮����Ҫʹ��ԭ�����@�R��AFM�����������ߌ����A�����M�Мy�����@һ���ַdz��P�I��

KLA �� Hiebert �f�������ڻ���I�ϣ��y���Ƕ���P�γɺ�ľ��A�����횲��Á��{���ȣ��Դ_���~���P���̵İ�Ҫ���~����I�ϵ���Ҫ��ˇ����������A����ȱ�ݿ��ơ����A����݆���{�������Լ�����픲��͵ײ�оƬ�ϵ��~���P�Č��ʡ��S������I��׃С�����羧�A�����A�g��С�� 2��m ����Ƭ�����A�g��С�� 10��m���@Щ����ȱ�ݡ�����݆�����I�Ϻ��P��������׃�ø�����Ҫ����

���^�@����߀������ijЩ�r��߀�����]��̽�y��FormFactor �������� Amy Leong ��ʾ�������y���J��ֱ�����~���P���~�K���M��̽�y�Dz����ܵģ������̽ᘼ�˺��K֮�g���ַ�����늽��|����Ҫ�Pע�����c����

��ˣ�FormFactor �_�l��һ�N���� MEMS ��̽��OӋ���Q�� Skate���Y�ϵͽ��|������˕��p��ش��^�����ӣ��Ķ��c�K�γ�늽��|��

���Ӌ�����E��߀��Ҫ�����A�M���坍���˻�̎����Ȼ����ʹ�õ�Ƭ���[�μ����и�ϵ�y�ھ��A���и�оƬ���@���a�����ڷ��b�Ć���Ƭ����Ƭ�и�O�������ԣ����и���t���a���w������Ⱦ���߅��ȱ�ݡ�

KLA �� Hiebert �f����������Ƭ֮�g�Ļ���I�ϣ����A�и����Ƭ̎���������~����w�����aԴ����회����M�й��������ھ��A����Ⱦ�̶ȵ͵ö࣬��������о������A�����A�M���x���и�Ļ���I�Ϸ�������

�и�֮����ճ�ϣ��@һ���E��Ҫʹ�õ��bоƬ�I�ϙCֱ�ӏ��и�����ʰȡоƬ��Ȼ��оƬ�����������A������оƬ�ϣ��@�ɂ��Y���ڳ����������Y�ϡ����~����I���У�оƬ�A��ʹ��늽��|�I�ϣ����M�н��ٻ��B��

ճ���^�̌�ճ�τ��Č��ʾ������������ijЩ��r�£����ʾ�����Ҫ�_�����ף��I��һ����Ҫ�_�������e��

���M����Ƭ�Č�����һ����𣬵����bоƬ�I�ϙC�ѽ���ǰ�~��һ����EV Group �� Uhrmann �f�������A�g�I�����������w��С�� 100nm �ķ���lչ����˷������M���c��Ҫ������Ƭ�����A��ͨ�����Ⱥ����a��֮�g������ه�Pϵ�������^�ߵľ��ȿ���ͨ�^�^�͵Ŀ��w���a����ƽ�⡣���ڹ����ѽ�ᘌ��T�纸�Ӻ͟ቺ�B��֮ĺ�˹�ˇ�M���˃�������� 1��m ��Ҏ���ں��Lһ�Εr�g�ܶ������ġ����ʽоƬ�����A�I�ϸ�׃���O���OӋ���@���ɾ��Ⱥ��O���坍������ģ���һ�����ߵ�Ҏ���h�h���� 500nm����

�I�����ڞ��@һĿ�˶�Ŭ������ ECTC �ϣ�BE �댧�w��˾��Besi��չʾ��һ�N�µĻ��оƬ - ���A�I�ϙCԭ�͵ĵ�һ헳ɹ�����KҎ��Ŀ�˞� 200nm��ISO 3 �����ҭh���Լ� 2000 UPH �� 300 mm ���A���塣ԓ�C������������A�_�����徧�A�_�Լ��R��ʰȡ�ͷ���ϵ�y��ԓ��˾��ʾ���C�����������a���̵���Ҫ�ԄӸ��Q����;��A�M�����Ҟ錍�F�߾��ȣ���˾�l�������ڿ��ٷ��̸߾��Ȍ��ʵĹ�WӲ����

���^����Ƭ���ʵ�̽����δֹͣ��������ܕ����F�µČ��ʆ��}��ȱ�ݣ��c���з��bһ�ӣ����ճ�ϵ� 2.5D �� 3D ���b������Ҫ���v����Ĝyԇ�͙z�鲽�E��

С�Y

����I����һ헿��еļ��g�����ܴ�����һaƷ�����^�͑���Ҫ������x���������еļ�����������һ���������顣 |